Design of an Aerospace-grade Radiation-hardened SRAM Cell for High-speed Read/Write Applications

-

摘要: 随着CMOS工艺微缩,静态随机存取存储器(SRAM)在宇航级场景下面临严峻辐射可靠性挑战,且现有抗辐射加固(RHBD)结构难以兼顾高抗辐射能力与高速读写访问性能。为此,该文提出一种面向高速读写需求的宇航级抗辐射SRAM单元RFWF16T。该结构通过双源隔离机制,将敏感节点缩减至2个;同时,通过构建对称的反馈回路,该单元实现了100%的单节点翻转自恢复与83.3%的双节点翻转自恢复。为突破传统加固结构的速度瓶颈,RFWF16T利用短反馈路径与低阻抗电压泄放回路,在28 nm工艺下实现了20.97 ps的读访问时间与2.72 ps的写访问时间,其读写速度相比其他8种同类典型加固结构分别平均提升了46.65%和14.77%。蒙特卡罗与工艺角-电压-温度实验表明,该结构在宽扰动范围内具有强鲁棒性,并在综合电气质量度量评价中表现最优。结果表明,RFWF16T在保证高抗辐射能力的同时有效解决了读写速度瓶颈,具备工程应用潜力。Abstract:

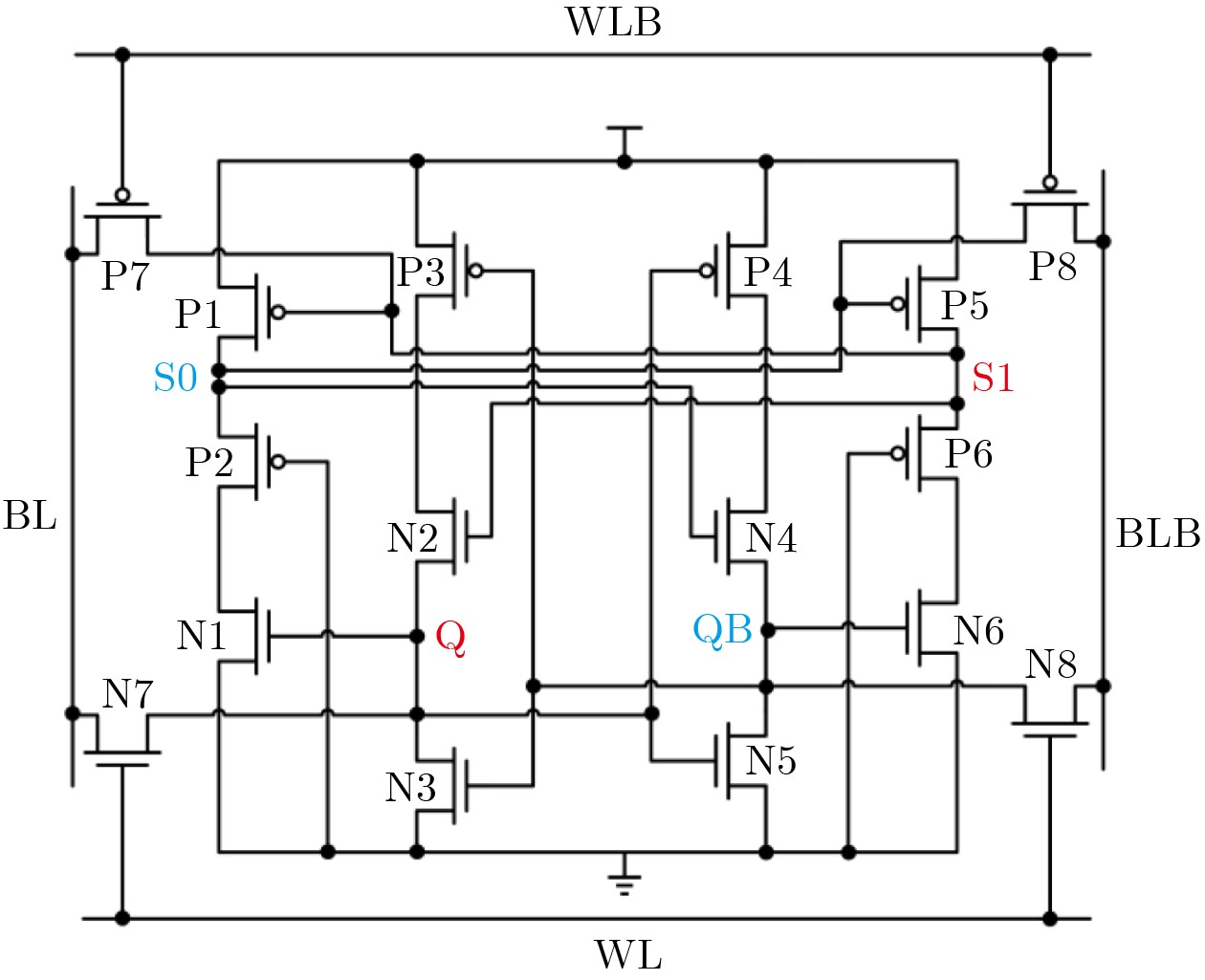

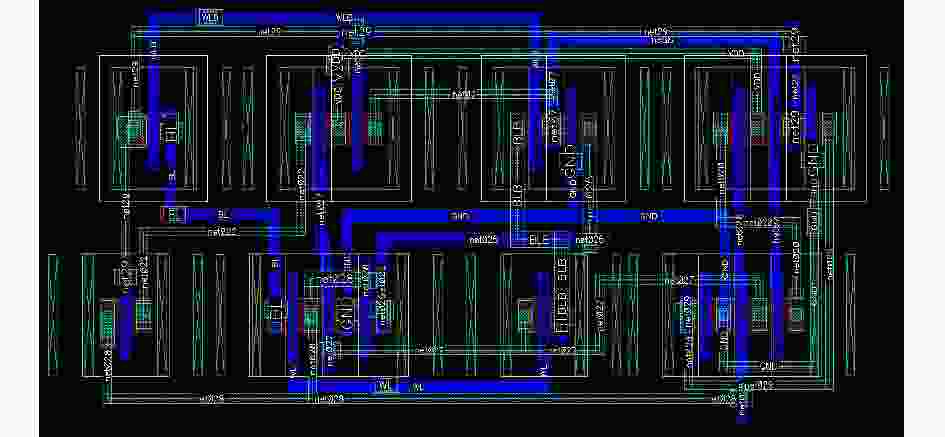

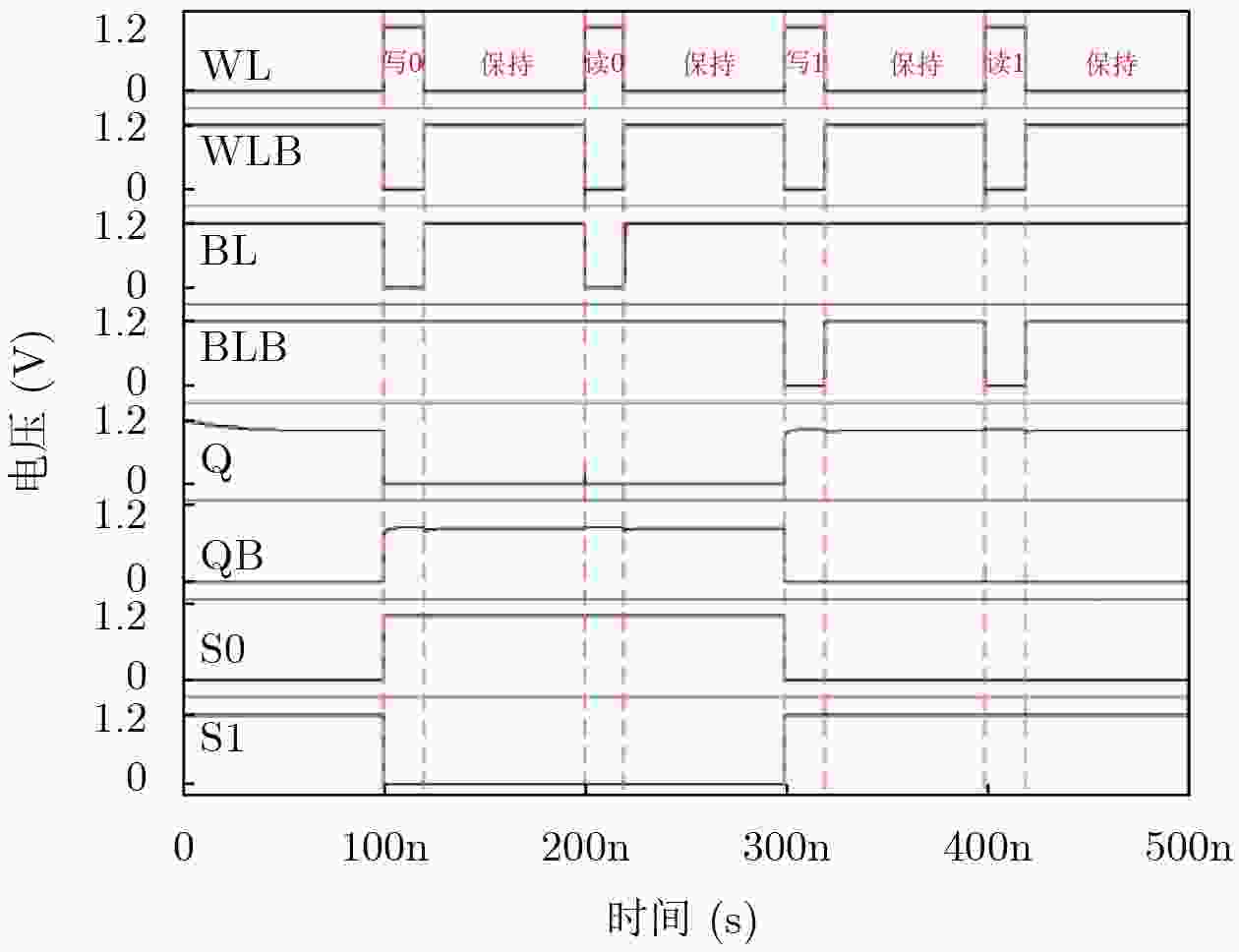

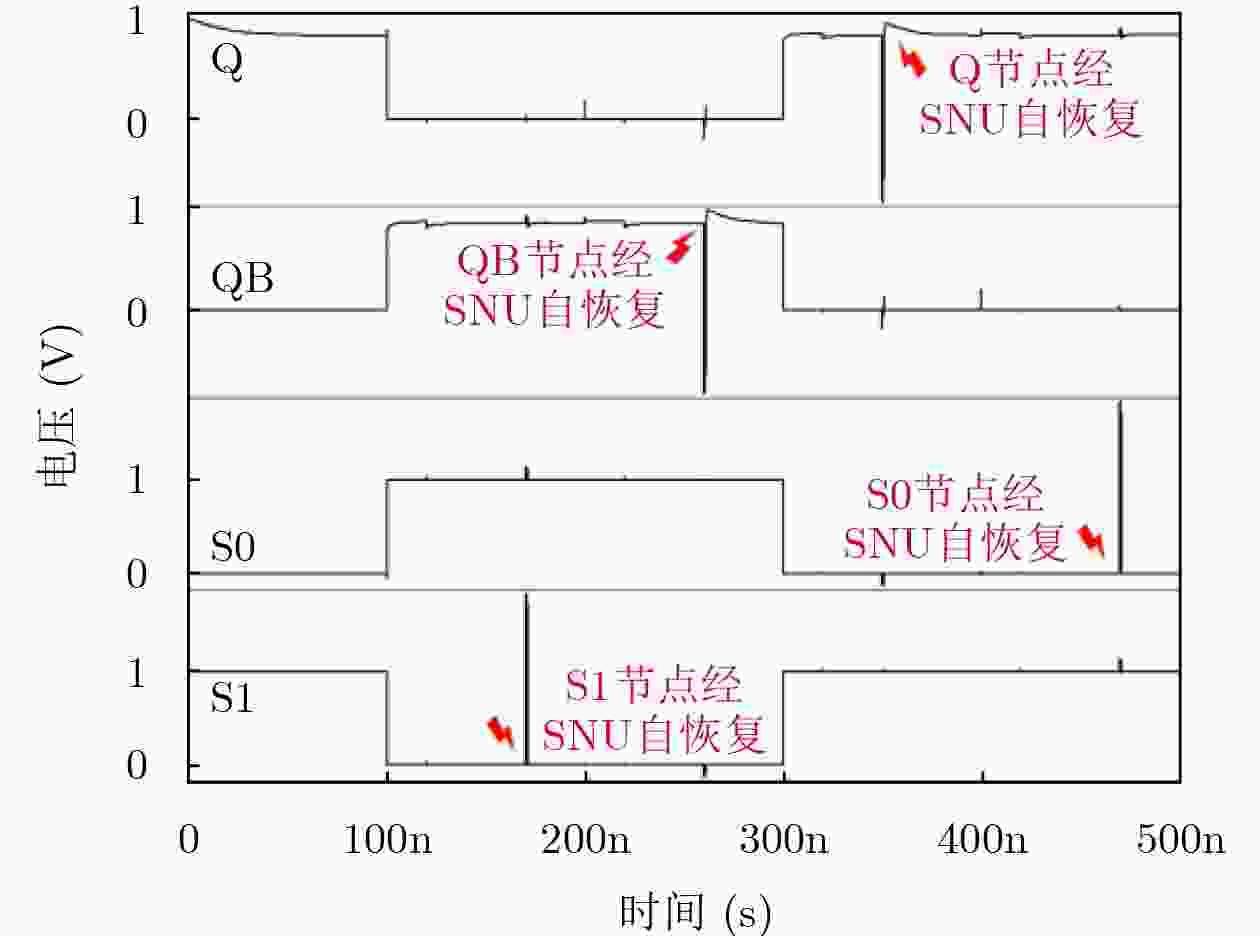

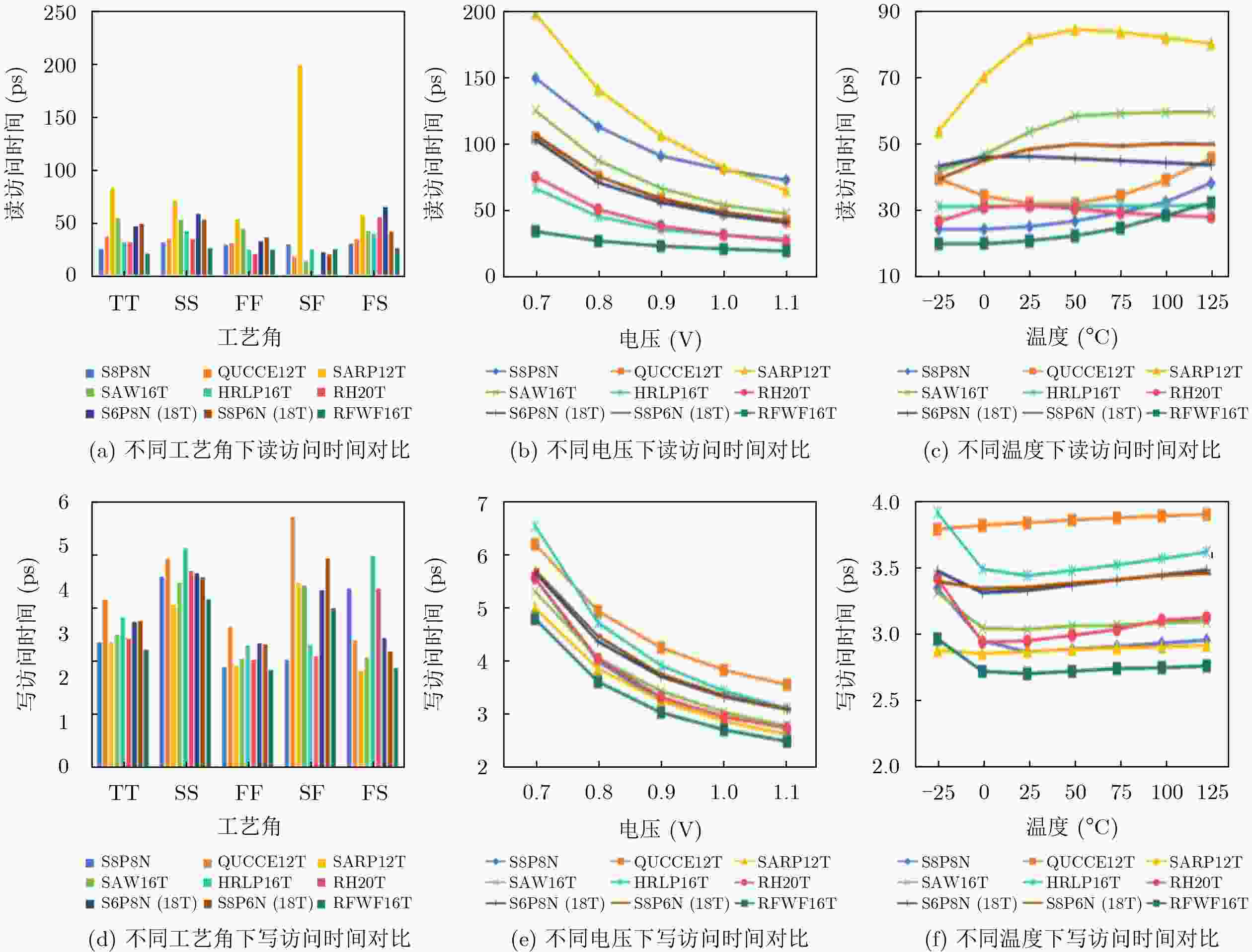

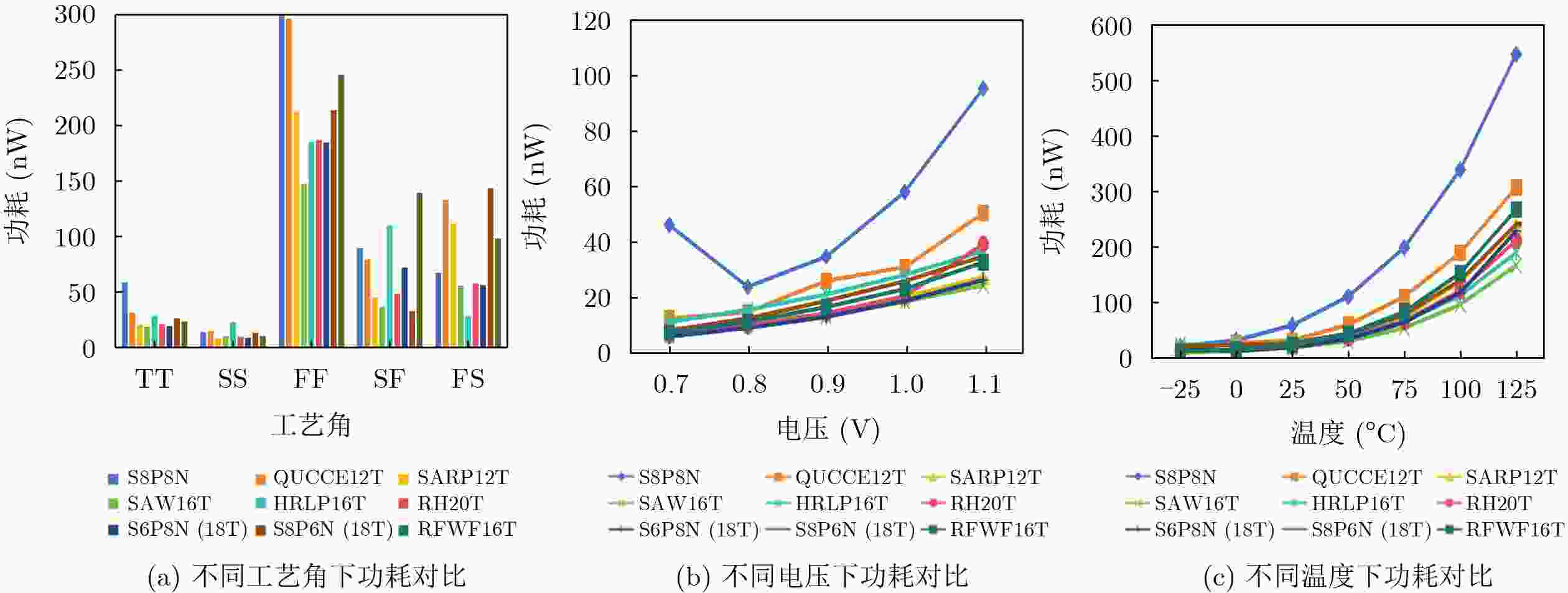

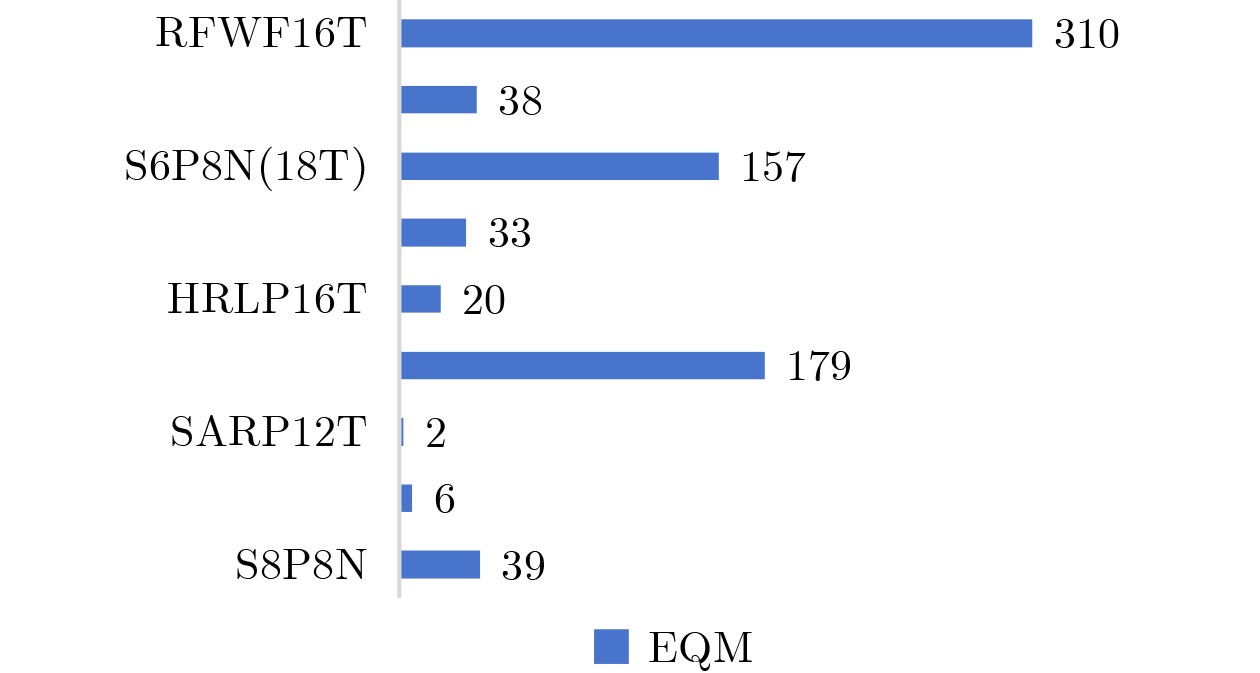

Objective With the continued scaling of Complementary Metal-Oxide-Semiconductor (CMOS) technology nodes and the reduction in supply voltage, Static Random Access Memory (SRAM) in aerospace environments becomes increasingly sensitive to high-energy particle radiation and is prone to Single-Node Upset (SNU) and Double-Node Upset (DNU). This sensitivity poses a serious challenge to the reliability of spaceborne Systems-on-Chip (SoC). Existing Radiation-Hardened-By-Design (RHBD) structures, however, usually cannot balance strong radiation tolerance with high-speed access performance. This work therefore aims to design an aerospace-grade radiation-hardened SRAM cell for high-speed read/write applications that provides both strong radiation resistance and fast access performance. Methods The proposed Read Fast and Write Fast 16-Transistor (RFWF16T) SRAM is built on a dual-source isolation architecture composed of 16 transistors (8 PMOS and 8 NMOS) ( Fig. 1 ,Fig. 2 ). By using a symmetric recovery mechanism, the RFWF16T reduces the number of key sensitive nodes to only two. Redundant transistors (P2 and P6) are used to establish a stable high-level isolation state, which isolates the storage nodes from potential disturbances during the non-access phase. To achieve high-speed operation, the RFWF16T combines a short feedback path with a low-impedance voltage discharge loop. Unlike conventional hardened cells that rely on stacked transistors, which increase resistance and delay, the RFWF16T adopts a parallel access topology connected to word lines and bit lines. This configuration forms a low-impedance path during write operations and significantly accelerates node voltage switching (Fig. 3 ). Performance verification confirms the self-recovery capability of the four data nodes. A comprehensive variation analysis is conducted, including Process-Voltage-Temperature (PVT) variations and 2,000-point Monte Carlo simulations. Additionally, an improved Electrical Quality Metric (EQM) is proposed to evaluate multidimensional performance quantitatively.Results and Discussions The RFWF16T exhibits strong overall performance, particularly in overcoming the speed bottleneck of hardened SRAM cells. In terms of access speed, the RFWF16T performs substantially better than typical models such as S8P8N, SAW16T, and RH20T. Under standard conditions (28 nm CMOS process, 1.0 V, 25 °C, TT corner), the RFWF16T achieves a Read Access Time (RAT) of 20.97 ps and a Write Access Time (WAT) of 2.72 ps. These values correspond to average speed improvements of 46.65% and 14.77%, respectively, over eight comparable hardened structures ( Table 2 ). PVT analysis confirms that the RFWF16T maintains the lowest latency across voltages from 0.7 V to 1.1 V and temperatures from –25 °C to 125 °C (Fig. 6 ). This write-speed advantage is attributed to the removal of write contention through optimized discharge paths. In terms of noise margin and stability, the RFWF16T demonstrates strong robustness and achieves the highest Write Word-line Toggle Voltage (WWTV) among nine comparative structures. Its Hold Static Noise Margin (HSNM) and Read Static Noise Margin (RSNM) also rank among the best, which ensures stability under disturbances (Fig. 7 ). In radiation hardening, the RFWF16T achieves a 100% self-recovery rate for SNUs and an 83.3% recovery rate for DNUs, reaching the state-of-the-art level among DNU-recoverable units (Table 1 ). Monte Carlo simulations confirm that the average recovery times of the internal nodes range from 1.09 ns to 1.19 ns (Fig. 4 ,Fig. 5 ). In terms of overhead, the RFWF16T maintains a normalized area of 1.00× (4.3 μm × 1.9 μm) (Table 3 ,Fig. 2 ) and an average power consumption of 23.45 nW (Table 4 ). Although the power consumption is slightly higher, this increase is a reasonable trade-off for the substantial speed advantage. In the EQM evaluation, the RFWF16T obtains the highest score, which confirms its overall advantage in balancing reliability, speed, and stability (Fig. 9 ).Conclusions A radiation-hardened SRAM cell, RFWF16T, is proposed for aerospace-grade high-speed read/write applications. The cell contains only two sensitive nodes and achieves 100% self-recovery for SNUs and an 83.3% recovery rate for DNUs, which demonstrates strong radiation tolerance. Compared with eight other SRAM cells, the RFWF16T significantly reduces read and write delay with only a slight increase in area and power consumption, while maintaining good noise immunity and the best electrical quality metric. PVT and Monte Carlo simulations further confirm the stability and robustness of the proposed cell under different operating conditions. Future work will focus on array-level integration and tape-out verification, and on its application in satellite-borne high-speed data processing. -

表 1 可靠性对比

表 2 标准测试下WAT与RAT对比

SRAM单元 RAT(ps) WAT(ps) PRCs(%) RAT WAT S8P8N[8] 25.36 2.88 –17.31 –5.42 QUCCE12T[9] 37.31 3.86 –43.80 –29.46 SARP12T[10] 83.06 2.88 –74.75 –5.46 SAW16T[11] 48.85 3.05 –57.07 –10.73 HRLP16T[12] 31.65 3.45 –33.74 –21.25 RH20T[13] 31.73 2.96 –33.91 –8.08 S6P8N(18T)[14] 46.89 3.34 –55.28 –18.59 S8P6N(18T)[14] 49.15 3.37 –57.33 –19.19 RFWF16T 20.97 2.72 –46.65(平均) –14.77(平均) 表 3 SRAM单元的归一化面积对比

-

[1] 魏肖彤, 许浩博, 尹春笛, 等. 天基计算芯片: 现状、趋势与关键技术[J]. 电子与信息学报, 2025, 47(9): 2963–2978. doi: 10.11999/JEIT250633.WEI Xiaotong, XU Haobo, YIN Chundi, et al. Space-based computing chips: Current status, trends and key technique[J]. Journal of Electronics & Information Technology, 2025, 47(9): 2963–2978. doi: 10.11999/JEIT250633. [2] 黄正峰, 李雪筠, 杨潇, 等. 一种新型低功耗加固SRAM存储单元[J]. 微电子学, 2021, 51(2): 157–162. doi: 10.13911/j.cnki.1004-3365.200196.HUANG Zhengfeng, LI Xueyun, YANG Xiao, et al. A novel low power radiation hardened SRAM memory cell[J]. Microelectronics, 2021, 51(2): 157–162. doi: 10.13911/j.cnki.1004-3365.200196. [3] 帅威, 蔡烁, 陈俊伊, 等. 宇航环境下基于RHBD的SRAM抗双节点翻转研究综述[J]. 集成电路与嵌入式系统, 2026, 26(3): 20–33. doi: 10.20193/j.ices2097-4191.2025.0097.SHUAI Wei, CAI Shuo, CHEN Junyi, et al. A review of RHBD-based SRAM design against double node upsets in space environment[J]. Integrated Circuits and Embedded Systems, 2026, 26(3): 20–33. doi: 10.20193/j.ices2097-4191.2025.0097. [4] ZHANG Deming, YANG Jiaxin, LUO Dingyi, et al. A 32 kb 55 nm radiation-hardened SRAM chip with SEU≤ 1.1 E-11 upsets/bit-day, SEL> 107.1 MeV⋅ cm2/mg, and TID> 100 Krad (Si) for space applications[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2025, 72(11): 6389–6398. doi: 10.1109/TCSI.2025.3565838. [5] 闫爱斌, 李坤, 黄正峰, 等. 两种面向宇航应用的高可靠性抗辐射加固技术静态随机存储器单元[J]. 电子与信息学报, 2024, 46(10): 4072–4080. doi: 10.11999/JEIT240082.YAN Aibin, LI Kun, HUANG Zhengfeng, et al. Two highly reliable radiation hardened by design static random access memory cells for aerospace applications[J]. Journal of Electronics & Information Technology, 2024, 46(10): 4072–4080. doi: 10.11999/JEIT240082. [6] 柏娜, 李钢, 许耀华, 等. 应用于航空航天领域的低功耗多节点抗辐射静态随机存取存储器设计[J]. 电子与信息学报, 2025, 47(3): 850–858. doi: 10.11999/JEIT240294.BAI Na, LI Gang, XU Yaohua, et al. Low-power multi-node radiation-hardened SRAM design for aerospace applications[J]. Journal of Electronics & Information Technology, 2025, 47(3): 850–858. doi: 10.11999/JEIT240294. [7] CALIN T, NICOLAIDIS M, and VELAZCO R. Upset hardened memory design for submicron CMOS technology[J]. IEEE Transactions on Nuclear Science, 1996, 43(6): 2874–2878. doi: 10.1109/23.556880. [8] BAI Na, XIAO Xin, XU Yaohua, et al. Soft-error-aware SRAM with multinode upset tolerance for aerospace applications[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2024, 32(1): 128–136. doi: 10.1109/TVLSI.2023.3328717. [9] JIANG Jiawei, XU Yiran, ZHU Wenyi, et al. Quadruple cross-coupled latch-based 10T and 12T SRAM bit-cell designs for highly reliable terrestrial applications[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2019, 66(3): 967–977. doi: 10.1109/TCSI.2018.2872507. [10] PAL S, KI W H, and TSUI C Y. Soft-error-aware read-stability-enhanced low-power 12T SRAM with multi-node upset recoverability for aerospace applications[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2022, 69(4): 1560–1570. doi: 10.1109/TCSI.2022.3147675. [11] BAI Na, ZHAO Weihao, XU Yaohua, et al. A low-energy critical charge-enhanced SRAM for aerospace applications[C]. 2024 IEEE International Test Conference in Asia (ITC-Asia), Changsha, China, 2024: 1–6. doi: 10.1109/ITC-Asia62534.2024.10661345. [12] YAN Aibin, XIANG Jing, HUANG Zhengfeng, et al. Design of a highly reliable and low-power SRAM with double-node upset recovery for safety-critical applications[C]. 2023 IEEE International Test Conference in Asia (ITC-Asia), Matsue, Japan, 2023: 1–6. doi: 10.1109/ITC-Asia58802.2023.10301170. [13] CAI Shuo, LIANG Xinjie, WEN Yan, et al. A radiation-hardened 20T SRAM Cell with high reliability and low power consumption[C]. 2024 IEEE International Test Conference in Asia (ITC-Asia), Changsha, China, 2024: 1–6. doi: 10.1109/ITC-Asia62534.2024.10661354. [14] CAI Shuo, LIANG Xinjie, HUANG Zhu, et al. Low-power and high-speed SRAM cells with double-node upset self-recovery for reliable applications[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2025, 33(2): 475–487. doi: 10.1109/TVLSI.2024.3466897. [15] BLACK D A, ROBINSON W H, WILCOX I Z, et al. Modeling of single event transients with dual double-exponential current sources: Implications for logic cell characterization[J]. IEEE Transactions on Nuclear Science, 2015, 62(4): 1540–1549. doi: 10.1109/TNS.2015.2449073. [16] ZHAO Qiang, PENG Chunyu, CHEN Junning, et al. Novel write-enhanced and highly reliable RHPD-12T SRAM cells for space applications[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2020, 28(3): 848–852. doi: 10.1109/TVLSI.2019.2955865. [17] PAL S, MOHAPATRA S, KI W H, et al. Design of soft-error-aware SRAM with multi-node upset recovery for aerospace applications[J]. IEEE Transactions on Circuits and Systems I: Regular Papers, 2021, 68(6): 2470–2480. doi: 10.1109/TCSI.2021.3064870. [18] BHARTI P K, PRASAD G, KUMAR M P, et al. DTQ-16T: Double node upset tolerant quadruple SRAM for space applications[C]. 2025 IEEE International Symposium on Circuits and Systems (ISCAS), London, United Kingdom, 2025: 1–5. doi: 10.1109/ISCAS56072.2025.11044171. [19] RAJI M and GHAVAMI B. Soft error rate reduction of combinational circuits using gate sizing in the presence of process variations[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2017, 25(1): 247–260. doi: 10.1109/TVLSI.2016.2569562. [20] REDDY B N K, SARANGAM K, VEERAIAH T, et al. SRAM cell with better read and write stability with Minimum area[C]. TENCON 2019–2019 IEEE Region 10 Conference (TENCON), Kochi, India, 2019: 2164–2167. doi: 10.1109/TENCON.2019.8929593. [21] HU V P H, FAN M L, SU P, et al. Analysis of GeOI FinFET 6T SRAM cells with variation-tolerant WLUD read-assist and TVC write-assist[J]. IEEE Transactions on Electron Devices, 2015, 62(6): 1710–1715. doi: 10.1109/TED.2015.2412973. [22] PENG Chunyu, HUANG Jiati, LIU Changyong, et al. Radiation-hardened 14T SRAM bitcell with speed and power optimized for space application[J]. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2019, 27(2): 407–415. doi: 10.1109/TVLSI.2018.2879341. [23] WEI Feng, CUI Xiaole, ZHANG Qixue, et al. Design of highly reliable 14T and 16T SRAM cells combined with layout harden technique[J]. IEEE Transactions on Device and Materials Reliability, 2024, 24(3): 390–400. doi: 10.1109/TDMR.2024.3417961. [24] PAL S, SRI D D, KI W H, et al. Soft-error resilient read decoupled SRAM with multi-node upset recovery for space applications[J]. IEEE Transactions on Electron Devices, 2021, 68(5): 2246–2254. doi: 10.1109/TED.2021.3061642. -

下载:

下载:

下载:

下载: